Siemens Digital Industrial Software has introduced Tessent™ RTL Pro, an innovative software solution designed to help integrated circuit (IC) design teams simplify and accelerate critical design for Testability (DFT) tasks for next-generation designs.

As IC designs continue to grow in size and complexity, engineers need to identify and address testability issues early in the design process. Siemens’ Tessent software can analyze and plug in most DFT logic early in the design process, perform rapid synthesis, run ATPG (Automatic test vector Generation), and enable the design process to be fully integrated. To find and resolve abnormal modules and take appropriate actions to meet the growing needs of customers.

Tessent RTL Pro further expands the design editing function of Tessent’s portfolio by automating the analysis and insertion of test points, wrapper units and X-bounding logic early in the design process, helping customers shorten the design cycle and improve the testability of the design. Unlike other solutions, Tessent RTL Pro can handle complex Verilog and SystemVerilog structures while maintaining the style of the original RTL design.

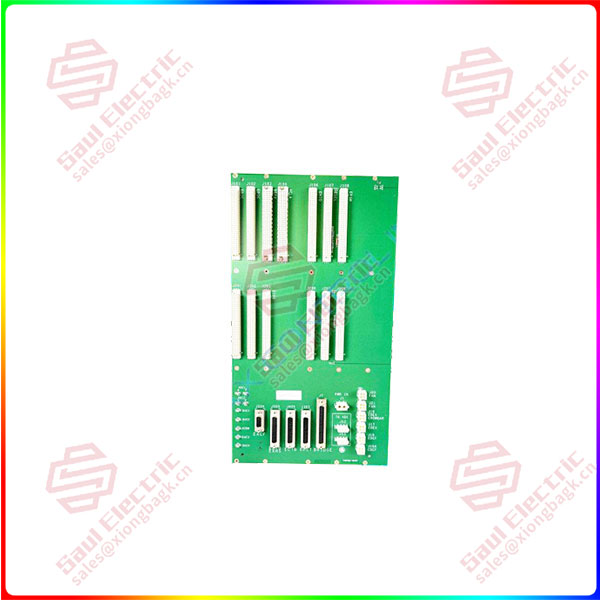

IS200ESBPG1A

Semiconductor company Renesas has adopted Tessent RTL Pro to advance its “Shift-left” work. Tatsuya Saito, Senior EDA Chief Engineer, Digital Design Technology Division, Shared R&D EDA Business Unit, Renesas Electronics Corporation, said: “Using Tessent RTL Pro for next generation automotive semiconductor design enables Renesas to continue its left-shift strategy and reduce the number of iterations in the traditional design process, and we can now not only achieve this goal, but also maintain best-in-class coverage and vector count.” Providing the backend and validation teams with the same complete design view that includes the Tessent IP, including the VersaPoint test points in RTL, is critical for Renesas to be competitive.”

The new solution, combined with the Siemens Tessent DFT tool, enables advanced functionality. Tessent RTL Pro analyzes the complexity of RTL and its adaptability to test point insertion to assess whether the user’s RTL structure can be edited efficiently. This is a key factor when adding test points throughout the design process, which can help users shorten the design cycle and speed products to market.

When adding DFT logic prior to synthesis, the “shift left” feature of Tessent RTL Pro helps enhance the ability of third-party tools to optimize area and timing, performing only scan chain insertion in a gate level circuit. Design insertion is carried out in the RTL development phase, utilizing RTL output to achieve seamless integration with third-party synthesis and validation software. In addition, the design documents generated by RTL Pro can be used with any downstream synthesis or validation process without the need for a closed process.

Ankur Gupta, Vice President and General Manager of Siemens Digital Industrial Software Tessent, said: “Tessent RTL Pro continues to deliver on Siemens’ mission to provide chip designers and DFT engineers with industry-leading solutions for their design processes. With the ability to analyze and insert wrapper units, X-bounding logic, and VersaPoint test points during the RTL phase of the design, customers can now significantly improve the testability of their designs, further advancing their left-shift plans.”

1 Year Warranty

1 Year Warranty