Description

Overview

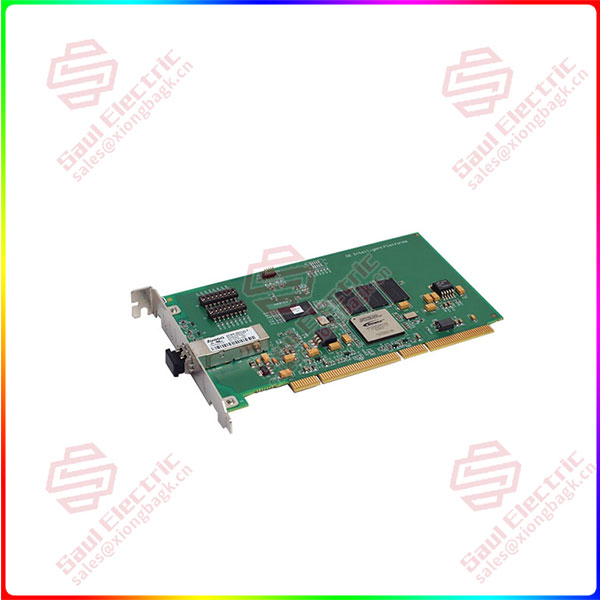

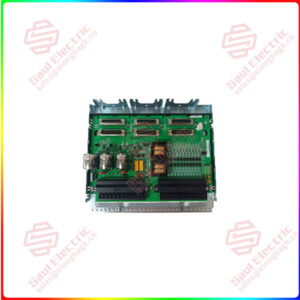

Essential details:PCI-5565PIORC-110000 Ultrahigh Speed Fiber-Optic Reflective Memory

lf you need to inquire or purchase ,please send the product models to my email or call medirectly .

sunny He

[Email] sales@xiongbagk.cn

[Mobile] 86-18059884797

[WhatsApp] 86-18059884797

[Skype] sales@saulcontrol.com

PCI-5565PIORC-110000 Ultrahigh Speed Fiber-Optic Reflective Memory

The classic VMlPMC-5565 contains several components which have beencombined into a single FPGA (Field Programmable Gate Array) in thePMC-5565PIORC, The components that were combined include a PCl interfacedevice by PLX Technologies, three separate smaller FPGAs, a transmit FlFO, anda receive FlFO.

The PMC-5565PIORC adds greater design flexibility and improved performanceover the classic VMIPMC-5565 in at least three areas.

1. The PMC-5565PIORC’s DMA burst and PlO single read access rates have animprovement over the classic VMIPMC-5565.

2. The PMC-5565PIORC’s access bandwidth for the onboard SDRAM memoryhas doubled, improving the overall throughput.

3. The PMC-5565PIORC is field upgradeable as new features are added.The classic VMlPMC-5565 contained a group of control registers within the PLXdevice as well as a separate group of RFM specific control registers located in anFPGA. Because the two registers groups physically reside in separate devices,they are accessed through different regions of memory, The PMC-5565PIORC, onthe other hand, contains both groups of registers within the same FPGA. The twogroups could have been combined, However to provide software continuity andbackward compatibility, the two register groups have been maintained separatelyas in the classic VMlPMC-5565. Further, the individual bit functions within theregisters, where applicable, are still compatible.

The PMC-5565PIORC does not include a second DMA engine.

1 Year Warranty

1 Year Warranty