Codasip®, the leader in RISC-V custom computing, announced: The company now offers its custom RISC-V processor cores the Tessent™ Enhanced Trace Encoder solution, a member of Siemens EDA’s Tessent Embedded Analytics embedded Analytics product line. With this joint solution, developers can effectively track and debug issues between chips and software, and can accurately understand the real-time behavior of the most complex custom designs based on the Codasip RISC-V processor™ processor.

Codasip’s RISC-V processors are fully customizable and can be fully adapted to the unique needs of the application. System designers can use the Codasip Studio™ toolchain to find the best software and hardware tradeoffs and achieve optimal functionality and PPA (power, performance, area). The combination of customizable processor IP and tools for processor design enables an automated approach to custom computing. To make this custom service available to software developers, Codasip ensures that all tools support customization, including compilers and debuggers. Tracking solutions are now included.

Adding tracking capabilities to SOCs can greatly speed up the once time-consuming task of software debugging, thereby reducing project start-up time and software development costs. Codasip chose to partner with Siemens EDA to develop its Trace Encoder because both companies share a strong belief in effective product quality throughout the product design process. This focus on quality enables innovation that can help customers significantly increase productivity even in the most complex heterogeneous and custom designs.

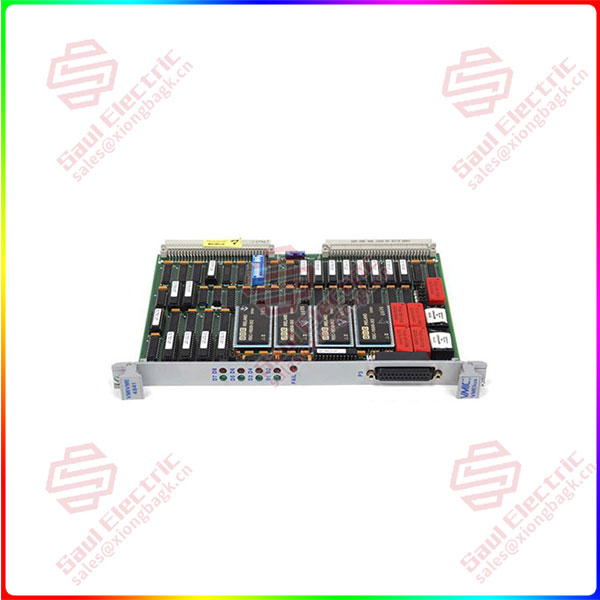

VMIVME-4941

The Tessent Enhanced Trace Encoder is based on the RISC-V standard developed by the Debug and Trace Working Group, which is led by representatives from Siemens, Siemens donated the Trace algorithm to the RISC-V international community. However, Siemens’ solution goes far beyond the RISC-V standard, providing a more efficient tool that offers significant productivity benefits in the development of the most complex systems, and also supports custom instructions. It performs a detailed examination of the system to find errors and their root cause. It is cycle-precise, which means that developers can gain insight into every instruction.

Mike Eftimakis, vice president of Strategy and Ecosystem at Codasip, commented: “Codasip holds its processor IP to a high standard of quality. To ensure that the results could support a great system, we needed a tracking solution that went beyond the RISC-V standard. The Tessent Enhanced Trace Encoder is optimized for the complex and customized systems our customers are developing.”

“Tessent Embedded Analytics enables real-time system-wide commissioning and post-deployment analysis, helping SoC providers focus on their mission-critical tasks of producing high-quality, innovative products and bringing them to market quickly.” Ankur Gupta, vice president and general manager of Siemens EDA Tessent. “Codasip has an excellent reputation for helping customers meet these requirements, and we are excited to partner with them.”

Codasip will provide Tessent Enhanced Trace Encoder solutions directly to customers to simplify contract complexity.

1 Year Warranty

1 Year Warranty